Automatic Code Generation

Automatic generation of control code

Related Tools

Related Modules

Related Brochures

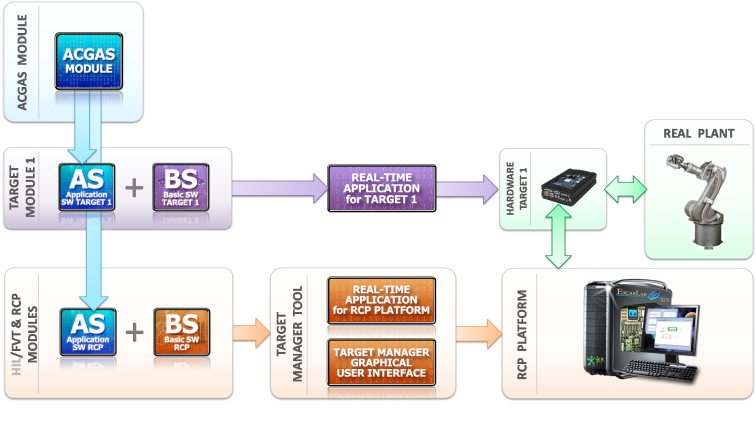

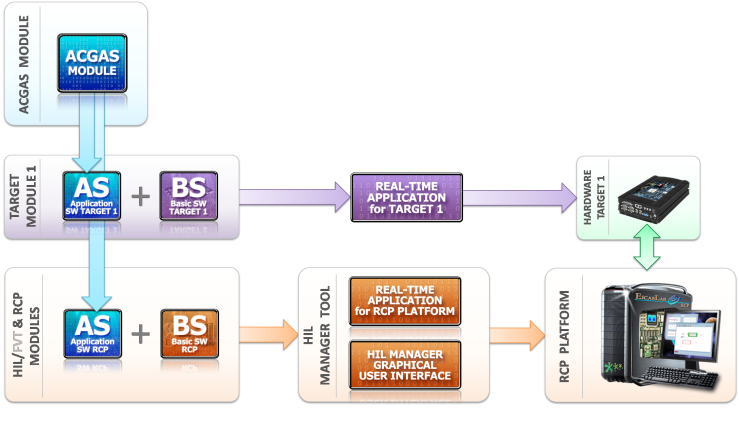

The final goal of EicasLab consists in generating the real-time software code to be transferred in the final hardware network of targets that will pilot the plant to be controlled.

The generated software code is subdivided in two main components:

- Application Software (AS), that represents the “target independent” part of the final code, implementing the control algorithm designed in EicasLab;

- Basic Software (BS), that represents the “target dependent” part of the final code: it schedules activities of each microprocessor, manages the microprocessor clock, the HW I/O interfaces, etc.

The EicasLab Automatic Code Generation (ACG) feature assists the control designer in generating the control software in all the control design phases, providing the following types of automatic code generation:

- ACG for AS, that generates only the code (AS) that implements the control algorithm. The AS is the same one that will run in the final HW target and in all the control design phases: Rapid Control Prototyping, Hardware-in-the-loop and Final Validation Test.

- ACG for RCP, that generates the code for performing the RCP activity by means of the RCP Manager tool (Rapid Control Prototyping operative mode).

- ACG for HW Target, that generates the code for the final target (Target operative mode).

- ACG for HIL, that generates the code for performing the Hardware-in-the-loop activity by means of the HIL Manager tool (Hardware-in-the-loop operative sub-mode).

- ACG for FVT, that generates the code for performing the Final Validation Test activity by means of the TARGET Manager tool (Final Validation Test operative sub-mode).

Automatic Code Generation Highlights

- Optimised automatic code generation feature

- Automatic code generation for:

- Application Software

- Rapid Control Prototyping

- Hardware Target

- Hardware-in-the-loop

- Final Validation Test

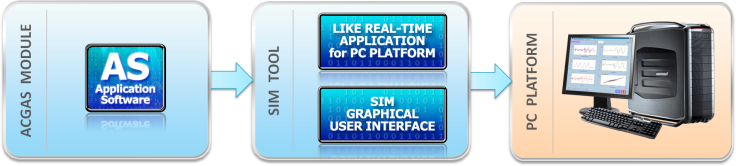

ACG for Application Software

The ACG for Application Software is the EicasLab feature aiming at generating in ANSI C language the AS of the designed control algorithm, optimised in order to be easily integrated with any Basic Software. This feature requires the ACGAS module.

The ACG for Application Software provides two advanced features:

- to test the generated AS - before transferring it in the final target - in a whole simulated environment by means of the SIM tool. The AS is the same one that will run in the final HW target and in all the control design phases: Rapid Control Prototyping, Hardware-in-the-loop and Final Validation Test. The designer can test and debug the AS not only during the simulation by means of the SIM tool, but also:

- during the real-time execution of the code performed in Rapid Control Prototyping by means of the RCP Manager tool;

- during the offline repetition of the same code run during the real-time experimental trial by means of the Slow Motion tool;

- to export the Application Software (AS) that can be easily integrated with the Basic Software (Application Software Export feature).

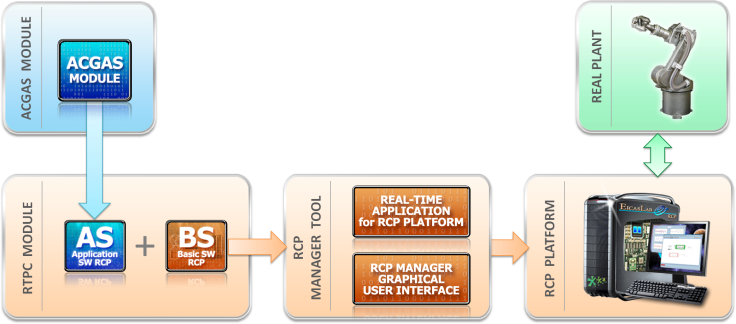

ACG for Rapid Control Prototyping

The ACG for Rapid Control Prototyping (RCP) is the EicasLab feature aiming at generating the BS which, combined with the AS generated by the ACGAS module, allows to manage the RCP activities through the RCP Manager tool.

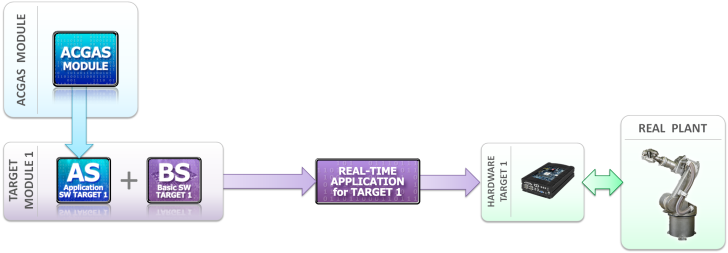

ACG for Hardware Target

The ACG for HW Target is the EicasLab feature aiming at generating the target-dependent source code for a set of pre-selected targets.

ACG for Hardware-in-the-loop

The ACG for HIL is the EicasLab feature aiming at generating the BS which, combined with the AS generated by the ACGAS module, allows to perform the Hardware-in-the-loop activities through the HIL Manager tool.

ACG for Final Validation Test

The ACG for FVT is the EicasLab feature aiming at generating the BS which, combined with the AS generated by the ACGAS module, allows to perform the Final Validation Test activities through the TARGET Manager tool.